User:Xjmaas: Difference between revisions

Jump to navigation

Jump to search

| Line 35: | Line 35: | ||

File:Ref n ROM CE.png|Reference n_ROM_CE | File:Ref n ROM CE.png|Reference n_ROM_CE | ||

File:Ref n ROM OE.png|Reference n_ROM_OE | File:Ref n ROM OE.png|Reference n_ROM_OE | ||

File:Ref n CFFF.png|Reference n_CFFF | File:Ref n CFFF.png|Reference n_CFFF (ignore unconnected pin) | ||

File:Ref PHI2.png|Reference for PHI2 clock regeneration | File:Ref PHI2.png|Reference for PHI2 clock regeneration | ||

</gallery> | </gallery> | ||

Revision as of 02:36, 5 July 2019

Personalia

An Apple Enthousiast since 1983 when we first obtained a bare Apple II logic board for which we (me and my dad) created a custom case. At the top of my collection I had several Apple ]['s and ///'s, a whole bunch of interface cards, several ProFiles and meters of software. Unfortunately this has been given to others in the past.

Currently I have a few (obtained a few years back) IIgs's, 3 working //c's and a Macintosh Colour Classic.

Right now I am working at a school in The Netherlands as ICT Coordinator.

Projects

The Apple II is a renewed hobby of mine and I have set my self to the following projects

Apple ][ Slot connector symbol and footprints I designed for Kicad and Eagle

Status

- active

Description

- I created these as I started my first projects with designing some boards for the Apple

File(s)

Apple ][ Multi Media Card (MMC) Mass Storage card

Status

- active

Description

- Board - Preliminary board design is done and a few bare boards have been ordered.

- CPLD - CPLD implementation is incomplete, I still lack some knowledge of VHDL to get some basic signals to work. The CPLD I use, is the Xilinx XC9572XL, as that is a 3.3V CPLD, but with 5V tolerant inputs.

- ROM - A basic ROM has been had working with a breadboard like environment.

My goal is to create an expansion card which uses the Multi Media Card SPI interface, based on the SPI65/B by André Fachat

(which in turn is a VHDL reimplementation of Daryl Rictor's 65SPI) as a (raw) mass storage device.

Current Issues

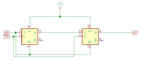

- In an effort to minimize the count of components, I opted to include the chip select logic for the EEPROM into CPLD, there should be some room left. For this I have to develop some simple (sub)entities for the VHDL project. I didn't get it right for now, but I have included some reference designs (made in Kicad). These still have to be (re)written in VHDL

-

Reference n_ROM_CE

-

Reference n_ROM_OE

-

Reference n_CFFF (ignore unconnected pin)

-

Reference for PHI2 clock regeneration

File(s)

Apple Plotter pens replica

Status

- On hold

Description

- At the moment this project has halted as I am trying to understand how to make "shell-like" models/objects this small using the 3D-printers we have at our school.